Eric Verhulst · Raymond T. Boute José Miguel Sampaio Faria Bernhard H.C. Sputh · Vitaliy Mezhuyev

# Formal Development of a Network-Centric RTOS

Software Engineering for Reliable Embedded Systems

Formal Development of a Network-Centric RTOS

Eric Verhulst • Raymond T. Boute José Miguel Sampaio Faria • Bernhard H.C. Sputh Vitaliy Mezhuyev

## Formal Development of a Network-Centric RTOS

Software Engineering for Reliable Embedded Systems

Eric Verhulst Altreonic NV Gemeentestraat 61AB1 B3210 Leuven, Belgium Eric.Verhulst@lancelot.be

José Miguel Sampaio Faria Rua Sra das Boas Novas 776 4935-490 Mazarefes Portugal imfaria@criticalsoftware.com

Vitaliy Mezhuyev Open License Society Zavelstraat 160 3010 Leuven Belgium Vitaliy.Mezhuyev@openlicensesociety.org Raymond T. Boute Department of Information Technology Universiteit Gent Faculty of Engineering St. Pietersnieuwstraat 41 9000 Gent Belgium boute@intec.UGent.be

Bernhard H.C. Sputh Open License Society Zavelstraat 160 3010 Leuven Belgium bernhard.sputh@openlicensesociety.org

ISBN 978-1-4419-9735-7 e-ISBN 978-1-4419-9736-4 DOI 10.1007/978-1-4419-9736-4 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2011933844

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### Preface

How can one improve with a factor of 10 on something that has already the reputation of being highly optimised? The answer lies in ignoring the most often wrong assumption that it is already highly optimised and by going back to basics. This inevitably includes developing a new formalisation of the problem at hand. In our case, this meant thinking anew about what a distributed RTOS (Real Time Operating System) is all about. What is the core functionality of an RTOS, of a distributed RTOS? Is there a clean way to handle task synchronisation and communication? The result was the unique network-centric OpenComRTOS project described in this book.

Taking this as an opportunity, we wanted to use formal methods to prove the final implementation. It turned out that formal methods can help to prove an implementation, but they really shine when used to model the architecture at an abstract level before any implementation is done. Their use has shown us again how much we are all influenced by what we know. After all our brains have a hard time reasoning without prior knowledge. Hence, our brains tend to look for known patterns so that known rules can be applied.

Looking for better and new solutions is hampered by prior knowledge. Formal methods help us because they allow us (or some would say: force us) to think at a more abstract level, our vision being less cluttered by implementation details. The result obtained in the project was a very clean and scalable architecture while verification had almost become trivial. There is also a general assumption that trustworthy means complex and large. Great was the surprise, however, when we discovered it resulted in the opposite. The RTOS was measured to be up to 10 times smaller than a previously hand coded version that had been tweaked over several years and used in demanding systems. This means less resources and less power are needed. So, to make the world less energy-hungry, use formal methods.

This project has to some extent reinvented the very concept of what an RTOS is. It is a way to model, it is a way to simulate, it is a way to verify, it is a way to program in a scalable and portable way concurrent systems. But our quest does not stop. OpenComRTOS is also an enabler for new functionality that is still being researched while the book is being written. A lot of the work has to do with researching the correct semantics to support e.g. composability, dynamic resource scheduling and fault tolerance. Ultimately, it might result in new hardware.

Last but not least, formal methods have proven not to be so hard to use as it was assumed to be. The project also demonstrated the strength of team work. Communication in a well working team is ultimately the way to get rid of the assumptions our brains involuntary make. Formal methods again help by replacing intuition by abstraction. This book is not an academic one. It describes aspects that were explored during a real industrial project to develop a distributed RTOS from scratch using formal methods. Therefore it contains as well a broad discussion on the context in which such RTOS are used, as well as deep technical details of some of the formal models used. But as such, the description is not complete because it describes a project, not a theory.

The book is organised as follows: In the first two chapters, we sketch the domain of interest: trustworthy embedded real-time distributed systems. We discuss the challenges to develop applications and systems in this domain and why formal methods are becoming essential tools for the engineer working in this field. We derive from it the requirements and specifications for OpenComRTOS. In the following two chapters we look at what formal methods and tools are available and introduce TLA+/TLC that was finally selected and used in the project. Subsequently, we discuss the formal TLA+ models, as well as the architecture, of OpenComRTOS. We dwell a bit deeper on the interaction semantics and provide an overview of the code size and performance results. For the interested user the appendix includes a usage tutorial, as well as the mathematical and logic foundations behind temporal logics like TLA+. The appendix also contains the TLA+ and SPIN models used to compare both formalisms in Chap. 3.

For the interested reader, a free version of OpenComRTOS for PC is available from www.altreonic.com. This version also acts as a simulator and cross development environment for multi-node targets.

#### Acknowledgements

This work has been made possible by the support of many people and organisations:

- Alexander Keda for developing the verification models and code generators.

- Anatoliy Konovalenko for developing the RTOS unit tests.

- Andrey Nitsenko for developing the graphical event tracer.

- Annie Dejonghe for moral support and administrative support.

- Bernhard Sputh for managing the release of the product and porting the RTOS.

- Dimitry Panfilov for developing the first visual front-end and porting the RTOS.

- Gjalt De Jongh for his conceptual discussions and first implementations.

- José Miguel Faria for developing the first formal models.

Preface

- Raymond Boute for his deep knowledge of formal techniques.

- Vitaliy Mezhuyev for his meta-modelling input.

The project was also financially supported by IWT of the Flemish Region and Melexis NV. Melexis also provided the first target processor.

Linden

Eric Verhulst

## Contents

| Lis | st of ] | Figures                                                    | xv   |

|-----|---------|------------------------------------------------------------|------|

| Lis | st of ' | Tables                                                     | xvii |

| Pa  | rt I    | Trustworthy Embedded Systems                               |      |

| 1   | Int     | roduction: OpenComRTOS Role in a Unified Systems           |      |

|     | Eng     | gineering Methodology                                      | 3    |

|     | 1.1     | Introduction                                               | 3    |

|     | 1.2     | A Systematic Engineering Methodology Based                 |      |

|     |         | on Unified Semantics and Interacting Entities              | 6    |

|     | 1.3     | Interacting Entities for the Software Domain               | 9    |

|     |         | 1.3.1   Silicon Technology Advances                        | 10   |

|     |         | 1.3.2Silicon Technology Limitations                        | 10   |

|     |         | 1.3.3   The World Becomes Connected                        | 11   |

|     | 1.4     | A Link with the Work Plan in a Systems Engineering Project | 11   |

|     | 1.5     | System Engineering Methods and Engineering Standards       | 12   |

|     | 1.6     | Where Do Formal Techniques Fit in?                         | 13   |

| 2   | Rec     | uirements and Specifications for the OpenComRTOS Project   | 15   |

|     | 2.1     | Background of OpenComRTOS                                  | 15   |

|     | 2.2     | Early Requirements Derived from the Virtuoso RTOS          | 17   |

|     | 2.3     | Real-Time Embedded Programming                             | 19   |

|     |         | 2.3.1 Why Real-Time?                                       | 19   |

|     |         | 2.3.2 Why a Simple Loop Is Often not Enough                | 20   |

|     |         | 2.3.3 Superloops and Static Scheduling                     | 21   |

|     |         | 2.3.4 Rate Monotonic Analysis                              | 24   |

|     |         | 2.3.5 Priority based Scheduling in OpenComRTOS             | 26   |

|     |         | 2.3.6 The Issue of Priority Inversion and Its              |      |

|     |         | Inadequate Solution                                        | 27   |

|     | 2.4     | Next Generation Requirements                               | 29   |

| 2.5 | Top Le  | evel Requirements for OpenComRTOS              | 32 |  |  |

|-----|---------|------------------------------------------------|----|--|--|

| 2.6 | Specifi | cations Derived from Requirements              | 34 |  |  |

| 2.7 | System  | Systems and Application Grammar of OpenComRTOS |    |  |  |

|     | 2.7.1   | Base Principles and Definitions                | 36 |  |  |

|     | 2.7.2   | A Note on Typing Conventions                   | 37 |  |  |

|     | 2.7.3   | OpenComRTOS System and Application Grammar     | 37 |  |  |

|     |         |                                                |    |  |  |

#### Part II Formal Modeling Fundamentals

| 3 | The  | Choice of | of TLA <sup>+</sup> /TLC: Comparing Formal Methods | 45 |

|---|------|-----------|----------------------------------------------------|----|

|   | 3.1  |           | Methods Survey and Pre-Selection                   | 45 |

|   | 3.2  | Case St   | udy                                                | 46 |

|   |      | 3.2.1     | Introduction                                       | 47 |

|   |      | 3.2.2     | The Algorithm                                      | 47 |

|   |      | 3.2.3     | Remarks                                            | 49 |

|   |      | 3.2.4     | Drawbacks                                          | 49 |

|   |      | 3.2.5     | Related Work                                       | 50 |

|   | 3.3  | $TLA^+$ : | and TLC                                            | 51 |

|   |      | 3.3.1     | Overview                                           | 51 |

|   |      | 3.3.2     | Model Developed                                    | 53 |

|   | 3.4  | Promel    | a and SPIN                                         | 59 |

|   |      | 3.4.1     | Overview                                           | 59 |

|   |      | 3.4.2     | Model Developed                                    | 62 |

|   | 3.5  | Compa     | rison                                              | 66 |

|   |      | 3.5.1     | Matching of the Method to the Application          | 66 |

|   |      | 3.5.2     | Human Factors                                      | 66 |

|   |      | 3.5.3     | Widespread Utilization                             | 66 |

|   |      | 3.5.4     | Licensing/Distribution                             | 68 |

|   |      | 3.5.5     | Maturity                                           | 68 |

|   |      | 3.5.6     | Performance                                        | 68 |

|   |      | 3.5.7     | Interface                                          | 68 |

|   |      | 3.5.8     | Coverage of the Input Language                     | 68 |

|   |      | 3.5.9     | Bibliography                                       | 69 |

|   |      | 3.5.10    | Expressiveness                                     | 69 |

|   |      | 3.5.11    | Readability                                        | 70 |

|   |      | 3.5.12    | Reusability                                        | 71 |

|   |      | 3.5.13    | Scalability                                        | 71 |

|   |      | 3.5.14    | Level of Abstraction                               | 71 |

|   |      | 3.5.15    | Checking Possibilities                             | 72 |

|   |      | 3.5.16    | Coverage of the Lifecycle                          | 72 |

| 4 | Basi | c Forma   | l Specification in TLA <sup>+</sup>                | 73 |

|   | 4.1  |           | ction                                              | 73 |

|   |      | 4.1.1     | Goal: Awareness in Specifying Systems              | 73 |

|   |      | 4.1.2     | A Two-Step Approach                                | 73 |

|   |      |           |                                                    |    |

| 4.2 | Structu | re of TLA <sup>+</sup> Specifications      | 74 |

|-----|---------|--------------------------------------------|----|

|     | 4.2.1   | Basic Structure                            | 74 |

|     | 4.2.2   | Module Structure                           | 75 |

| 4.3 | Introdu | icing TLA <sup>+</sup> By Example          | 76 |

|     | 4.3.1   | Basic TLA <sup>+</sup> Notions             | 76 |

|     | 4.3.2   | Basic Examples: TLA <sup>+</sup> Sequences |    |

|     |         | and OpenComRTOS Lists                      | 77 |

|     | 4.3.3   | An Extended Example: The Module Port       | 79 |

| 4.4 | Conclu  | ision                                      | 85 |

#### Part III OpenComRTOS Design

| 5 | For  | mal Modelling of the RTOS Entities |              | 89 |

|---|------|------------------------------------|--------------|----|

|   | 5.1  | Introduction                       |              | 89 |

|   | 5.2  | OpenComRTOS Environment Mode       | 1            | 90 |

|   |      | 5.2.1 Term Definitions             |              | 91 |

|   |      | 5.2.2 Constants                    |              | 91 |

|   |      | 5.2.3 Variables Representing the S | System State | 92 |

|   |      | 5.2.4 The L1-Packet                | -            | 92 |

|   |      |                                    |              | 93 |

|   | 5.3  | Formal Model of the Semaphore-Ent  | tity         | 93 |

|   |      | _                                  |              | 94 |

|   |      | 5.3.2 Variables                    |              | 94 |

|   |      | 5.3.3 Initialisation               |              | 94 |

|   |      | 5.3.4 Signalling the Semaphore     |              | 95 |

|   |      | 5.3.5 Testing the Semaphore        |              | 97 |

|   |      | 5.3.6 Constraints                  |              | 00 |

|   |      | 5.3.7 Defining the Next State      | 1            | 01 |

|   |      | •                                  |              | 01 |

|   |      | -                                  |              | 02 |

|   |      | •                                  |              | 04 |

|   | 5.4  | Model Verification                 |              | 04 |

|   | 5.5  | Conclusion                         | 1            | 05 |

| 6 | Fina | al Architecture of the RTOS        |              | 07 |

|   | 6.1  | The Building Blocks of OpenComR    | ГОЅ 1        | 07 |

|   |      | • •                                |              | 08 |

|   |      | • •                                |              | 13 |

|   |      | 6.1.3 Packets                      |              | 14 |

|   | 6.2  | The Semaphore Loop                 |              | 15 |

|   |      |                                    |              | 16 |

|   |      | 6.2.2 Heterogeneous Multiproces    |              |    |

|   |      | e i                                |              | 18 |

|   | 6.3  | OpenComRTOS Development Proce      |              | 19 |

|   | 6.4  | Summary                            |              | 19 |

|   |      | 2                                  |              |    |

| 7 | Task | Interac                                  | tion Models in OpenComRTOS          | 121 |  |  |

|---|------|------------------------------------------|-------------------------------------|-----|--|--|

|   | 7.1  | Introdu                                  | action                              | 121 |  |  |

|   | 7.2  | 2 Modelling Task Interaction             |                                     |     |  |  |

|   | 7.3  | Timing Properties of Task Interactions 1 |                                     |     |  |  |

|   | 7.4  | Notes of                                 | on Asynchronous Interactions        | 128 |  |  |

|   | 7.5  | Conclu                                   | isions                              | 131 |  |  |

| 8 | Resu | ilts: Cod                                | le Size and Performance             | 133 |  |  |

|   | 8.1  | Metrics                                  | s of Success                        | 133 |  |  |

|   |      | 8.1.1                                    | Code Size                           | 134 |  |  |

|   |      | 8.1.2                                    | Total Memory Use                    | 137 |  |  |

|   |      | 8.1.3                                    | Influence of Processor Architecture | 137 |  |  |

|   |      | 8.1.4                                    | Semaphore Loop                      | 139 |  |  |

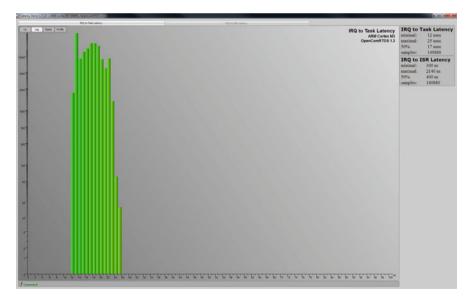

|   |      | 8.1.5                                    | Interrupt Latency                   | 139 |  |  |

|   |      |                                          |                                     |     |  |  |

#### Part IV Appendix

| Α | Oper | nComR     | ГОS-Suite 1.3 Usage Tutorial                    | 143 |  |

|---|------|-----------|-------------------------------------------------|-----|--|

|   | A.1  | Develo    | ping a Single Node Semaphore-Loop Project       | 143 |  |

|   | A.2  | Going l   | Distributed with OpenComRTOS                    | 153 |  |

|   | A.3  | Tracing   | g in OpenComRTOS                                | 155 |  |

|   |      | A.3.1     | How to Enable Tracing                           | 157 |  |

|   |      | A.3.2     | How to Retrieve a Trace                         | 158 |  |

|   |      | A.3.3     | Retrieving and Displaying Traces from           |     |  |

|   |      |           | Distributed Systems                             | 159 |  |

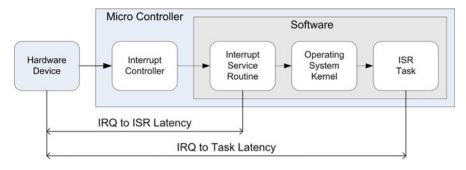

|   | A.4  | Measur    | ring the Interrupt Latency of OpenComRTOS       | 160 |  |

|   |      | A.4.1     | Designing Distributed Heterogeneous Systems     |     |  |

|   |      |           | Using the OpenComRTOS Suite                     | 160 |  |

|   |      | A.4.2     | Presenting the Measurement Results              | 162 |  |

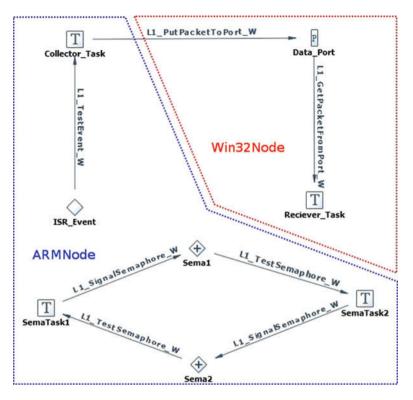

|   |      | A.4.3     | Specifying the System                           | 162 |  |

|   |      | A.4.4     | Implementation                                  | 164 |  |

|   |      | A.4.5     | Application                                     | 165 |  |

|   |      | A.4.6     | Collected Measurement Results                   | 166 |  |

|   | A.5  | Summary 1 |                                                 |     |  |

| B | Four | dations   | for TLA <sup>+</sup> and Temporal Logic         | 169 |  |

|   | B.1  |           |                                                 |     |  |

|   |      | B.1.1     | Goal: Increased Awareness in Specifying Systems | 169 |  |

|   |      | B.1.2     | Approach and Overview                           | 170 |  |

|   | B.2  | A Unif    | ying Formalism                                  | 171 |  |

|   |      | B.2.1     | Rationale                                       | 171 |  |

|   |      | B.2.2     | Syntax                                          | 171 |  |

|   |      | B.2.3     | Style of Use                                    | 173 |  |

|   |      | B.2.4     | Introducing <i>TLA</i> <sup>+</sup> Via Funmath | 178 |  |

|   | B.3  | Faithfu   | l Formalization of Informal Specifications      |     |  |

|   |      | B.3.1     | Choice of Proper Data Abstractions              |     |  |

|   |      |           | 1                                               |     |  |

|            |     | B.3.2              | Auxiliary Functions in Formal Specifications            | 184 |

|------------|-----|--------------------|---------------------------------------------------------|-----|

|            | B.4 | Calcula            | tional Reasoning and Patterns in TLA <sup>+</sup>       | 186 |

|            |     | <b>B.4.1</b>       | Capturing Temporal Logics by Temporal Calculi           | 186 |

|            |     | B.4.2              | A Functional Temporal Calculus (FTC)                    | 187 |

|            |     | B.4.3              | Defining the Temporal Calculus of Actions (TCA)         | 190 |

|            |     | B.4.4              | Calculational Reasoning in TCA/ <i>TLA</i> <sup>+</sup> | 192 |

|            |     | B.4.5              | Applications to Patterns in <i>TLA</i> <sup>+</sup>     | 194 |

|            | B.5 | Conclus            | sions                                                   | 196 |

| С          | Com | parision           | of Formal Methods                                       | 199 |

|            | C.1 | TLA <sup>+</sup> I | Model of Harris' Algorithm                              | 199 |

|            | C.2 | Promela            | a Model of Harris' Algorithm                            | 206 |

| Glossary   |     |                    |                                                         |     |

| References |     |                    |                                                         | 213 |

| Index      |     |                    |                                                         | 217 |

## **List of Figures**

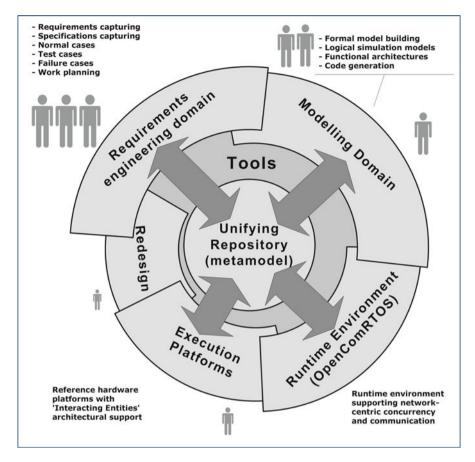

| Fig. 1.1 | Unified Systems Engineering Methodology                           | 7   |

|----------|-------------------------------------------------------------------|-----|

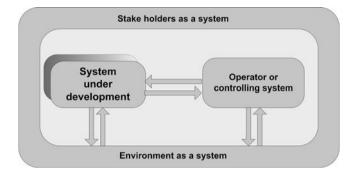

| Fig. 2.1 | The context of systems engineering                                | 16  |

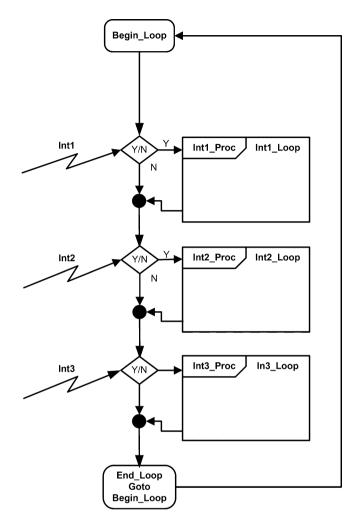

| Fig. 2.2 | Superloop schedule with three interrupt sources                   | 22  |

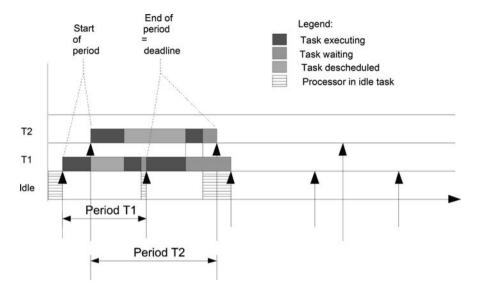

| Fig. 2.3 | Two periodic tasks scheduled with RMA                             | 24  |

| Fig. 2.4 | Three tasks sharing a resource with and without priority          |     |

|          | inheritance support                                               | 30  |

| Fig. 3.1 | Example of a specification in TLA <sup>+</sup>                    | 52  |

| Fig. 3.2 | <i>Header</i> of the TLA <sup>+</sup> model                       | 56  |

| Fig. 3.3 | Bottom of the TLA <sup>+</sup> Specification of Harris' algorithm | 57  |

| Fig. 3.4 | Definition of <i>Coherence</i>                                    | 57  |

| Fig. 3.5 | Definition of action CreateI                                      | 57  |

| Fig. 3.6 | Definition of action <i>LocateD</i>                               | 58  |

| Fig. 3.7 | Definition of action CasD2                                        | 59  |

| Fig. 3.8 | Comparison of the formalisms                                      | 67  |

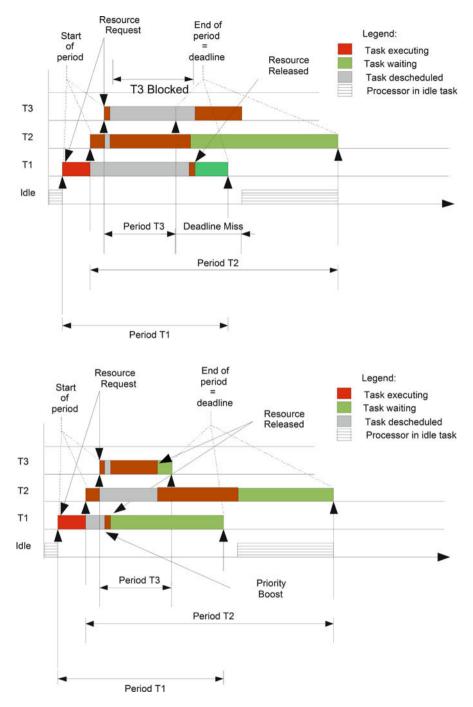

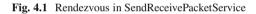

| Fig. 4.1 | Rendezvous in SendReceivePacketService                            | 83  |

| Fig. 6.1 | A simple OpenComRTOS application using Port Hubs                  | 108 |

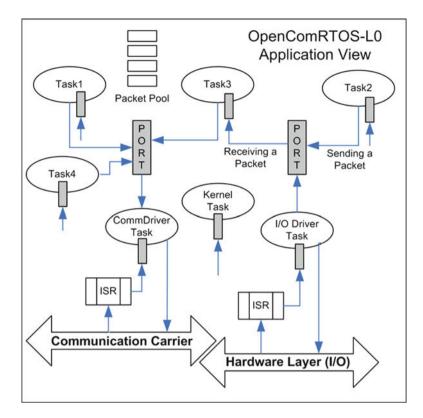

| Fig. 6.2 | Hub diagram                                                       | 109 |

| Fig. 6.3 | Application diagram with all Interactions for the                 |     |

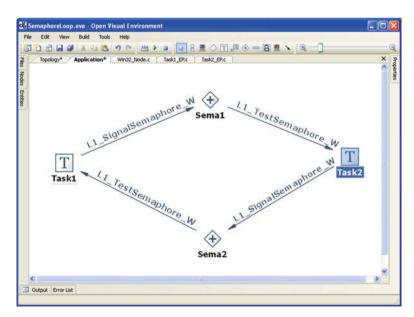

|          | Semaphore Loop                                                    | 115 |

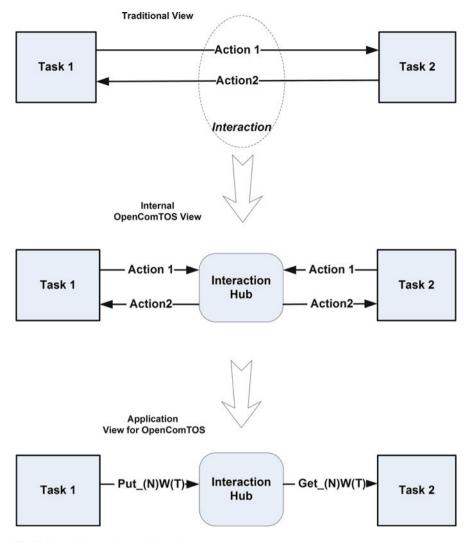

| Fig. 7.1 | Task interactions with a Hub                                      | 124 |

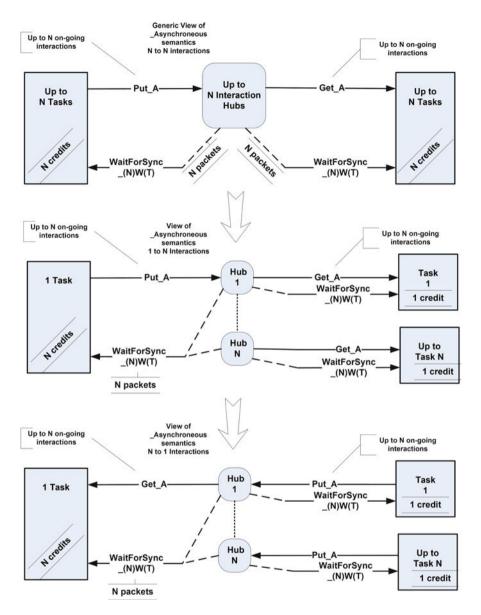

| Fig. 7.2 | Asynchronous Task interactions with Hubs                          | 129 |

| Fig. A.1 | Screenshot of OpenVE's the 'New Project' dialogue                 | 144 |

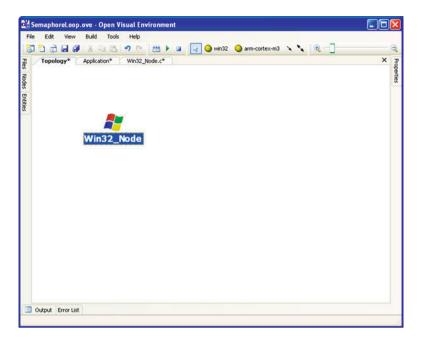

| Fig. A.2 | OpenVE with opened Topology View (no nodes defined yet)           | 145 |

| Fig. A.3 | The dialogue to specify the properties of the new win32-node      | 145 |

| Fig. A.4  | Topology view showing the newly created win32-node               | 146 |

|-----------|------------------------------------------------------------------|-----|

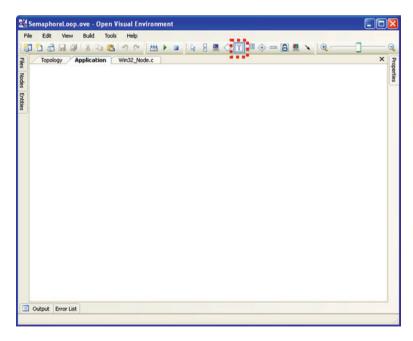

| Fig. A.5  | OpenVE Application Diagram with highlighted Task button          | 146 |

| Fig. A.6  | 'New Task' dialogue, with highlighted 'Task                      |     |

|           | Entrypoint' creation button                                      | 147 |

| Fig. A.7  | The Task Entrypoint creation dialogue, showing the               |     |

| •         | source code that will be generated                               | 147 |

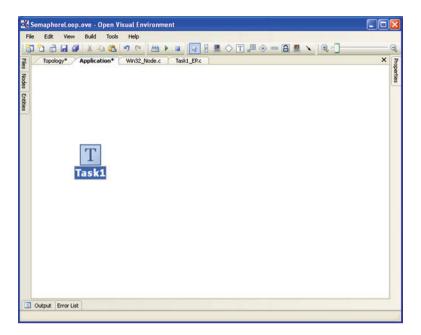

| Fig. A.8  | Application diagram showing the newly created Task1              | 148 |

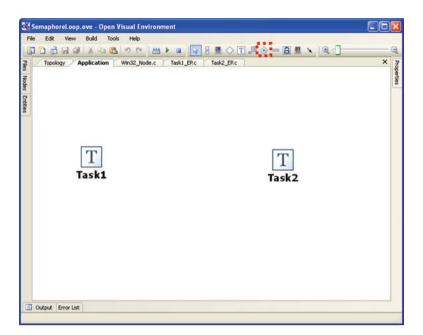

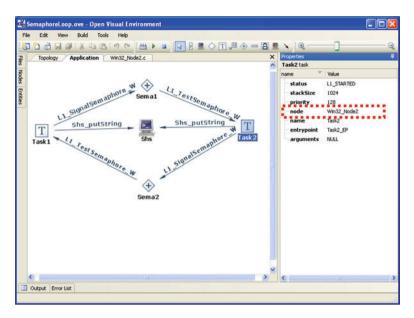

| Fig. A.9  | Application diagram showing both Task1 and Task2                 | 149 |

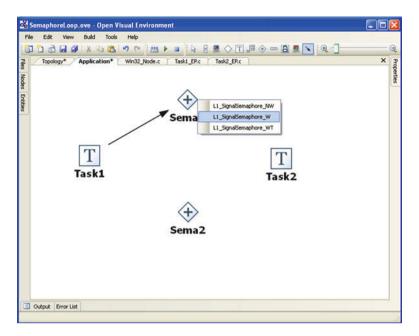

| Fig. A.10 |                                                                  | 149 |

| Fig. A.11 | Application diagram with all entities, showing the               |     |

| •         | interaction selection menu                                       | 150 |

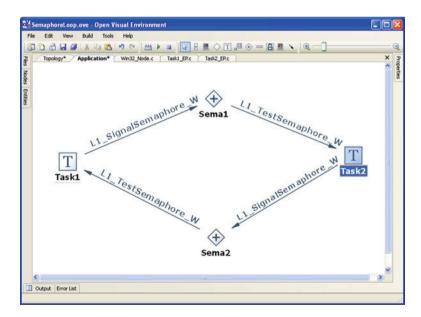

| Fig. A.12 | Application diagram with all Interactions for the                |     |

| •         | Semaphore Loop                                                   | 150 |

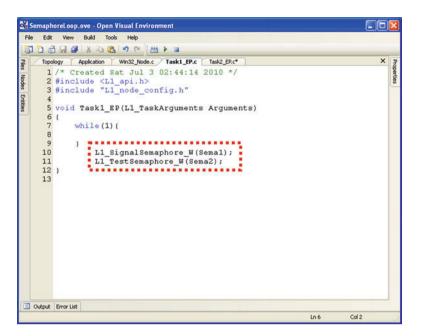

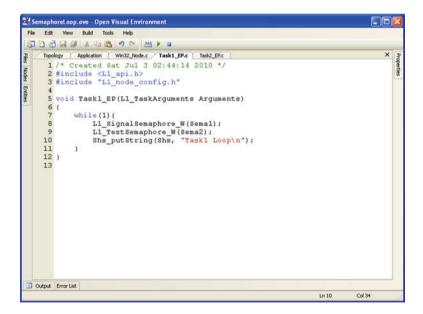

| Fig. A.13 | Source code for Task1, the incorrectly placed                    |     |

| •         | interactions highlighted                                         | 151 |

| Fig. A.14 | The 'New stdioHostServer' dialogue of OpenVE                     | 151 |

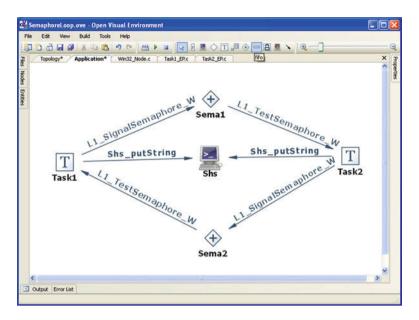

|           | Application diagram with the complete Semaphore-                 |     |

| •         | Loop and the Stdio Host Server                                   | 152 |

| Fig. A.16 | Source code of Task1 with Semaphore and Stdio Host               |     |

| •         | Server Interactions                                              | 152 |

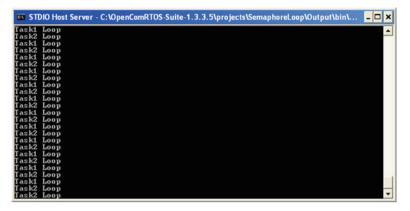

| Fig. A.17 | Console output upon running the 'SemaphoreLoop' project          | 153 |

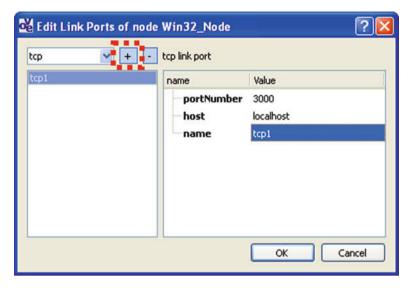

| -         | Edit Link Ports Dialogue, with highlighted 'Add Link             |     |

| •         | Port' button                                                     | 154 |

| Fig. A.19 | OpenVE link configuration dialogue                               | 154 |

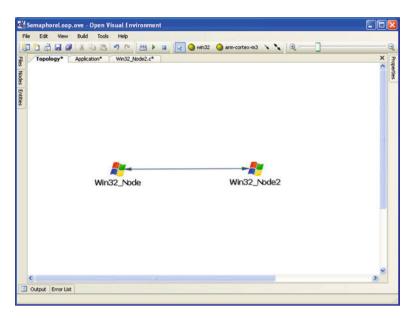

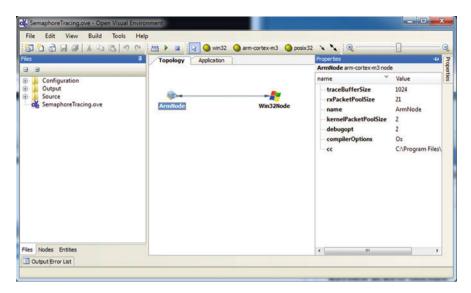

| Fig. A.20 | Topology of the two Win32 Nodes connected with a                 |     |

| •         | bidirectional Link                                               | 155 |

| Fig. A.21 | OpenVE with open 'Properties' side-pane and                      |     |

| •         | highlighted 'node' property                                      | 156 |

| Fig. A.22 | Console output of both win32-nodes                               | 156 |

| Fig. A.23 | OpenVE with open Property Pane                                   | 157 |

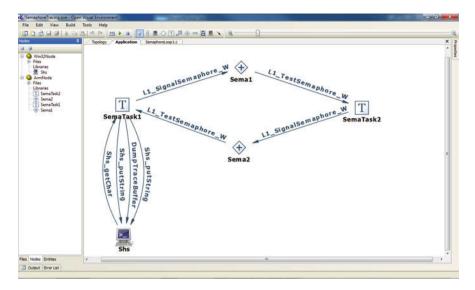

|           | Tracing enabled Application Diagram                              | 159 |

| -         | OpenTracer displaying parts of the                               |     |

| •         | SemaphoreTracing_MP_TCPIP example trace                          | 159 |

| Fig. A.26 | Stages of IRQ handling in a typical Microcontroller System       | 161 |

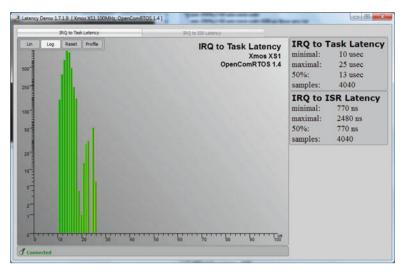

| Fig. A.27 | Screenshot of the Interrupt Latency GUI Application              | 164 |

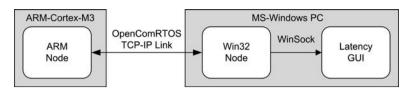

|           | Interrupt latency measurement system topology                    | 165 |

| Fig. A.29 | Interrupt latency measurement system application diagram         | 166 |

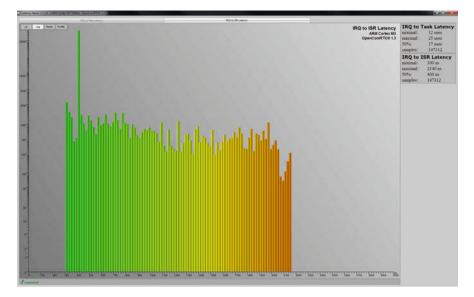

| Fig. A.30 | Measured IRQ to ISR Latency on ARM Cortex M3                     |     |

|           | 50MHz (logarithmic scale)                                        | 167 |

| Fig. A.31 | Measured IRQ to Task Latency on ARM Cortex M3                    |     |

| -         | 50MHz (logarithmic scale)                                        | 167 |

| Fig. B.1  | Numbers of beans                                                 | 182 |

| Fig. B.2  | Bag of beans                                                     | 183 |

| Fig. B.3  | The <i>Bags</i> module from <i>Specifying Systems</i> compressed | 185 |

| 0         | G F F G G G G G G G G G G G G G G G G G                          |     |

## **List of Tables**

| Table 3.1 | Correspondence of TLA <sup>+</sup> model with the textual description in Sect. 3.2.2 | 57  |

|-----------|--------------------------------------------------------------------------------------|-----|

| Table 7.1 | Time semantics of two Tasks interacting in                                           |     |

|           | OpenComRTOS                                                                          | 126 |

| Table 8.1 | Code size for OpenComRTOS kernel on MLX16                                            | 135 |

| Table 8.2 | Total memory used for OpenComRTOS on MLX16                                           | 138 |

| Table 8.3 | Code size figures (in 8 bit Bytes)                                                   | 139 |

| Table 8.4 | Semaphore Loop times ( $=2$ signals, 2 tests, 4 context                              |     |

|           | switches) in microseconds                                                            | 139 |

| Table B.1 | Basic mathematical TLA <sup>+</sup> expressions via Funmath                          |     |

|           | equivalent, part 1                                                                   | 179 |

| Table B.2 | Basic mathematical TLA <sup>+</sup> expressions via Funmath                          |     |

|           | equivalent, part 2                                                                   | 180 |

| Table B.3 | Action and temporal operators of TLA <sup>+</sup> defined via Funmath                | 180 |

## Part I Trustworthy Embedded Systems

### Chapter 1 Introduction: OpenComRTOS Role in a Unified Systems Engineering Methodology

OpenComRTOS is part of a systematic, formalised systems and software engineering methodology for embedded systems with a supporting environment and tools. While OpenComRTOS can be used independently of it, users will benefit from using the methodology in an integrated way. This methodology is characterised by two key concepts: unified semantics and interacting entities. When used in combination, they result in a better control of the engineering process leading to the development of systems and products. OpenComRTOS plays an important role in this approach as it is the system software layer allowing the mapping of the abstract interacting entities at the modeling level into concrete concurrent instances.

#### 1.1 Introduction

Our economy, our social and political environment can be considered as a system of systems. As citizens, we want these systems to work for us and to improve our lives. Technology and engineering are playing a growing and important role in it. The main reason for this fact is that technology allows us to do more with less. Technology provides us with efficiency. The task of the engineer is to put technology at work and to develop systems and products that provide us with added value. This applies to many domains, even in domains where technology only plays a supporting role and the role of the human is still dominant.

The authors of this book are mostly concerned with the domain of so-called embedded systems. While there is no unique definition for this domain, think about it as the domain of devices and systems that have a processor and software inside, often fully invisible to the user. It came into being when the transistor was invented. This was the start of the digital electronics era. Digital implies that it became more and more practical for engineers to start building systems based on the concept of state machines. What the solid-state transistor changed was that because of its shrinking size, many of these components could be used together to build very large scale state machines. A typical example is the processor in a desktop PC, now containing several of such devices, each having close to a billion transistors. Even a small processor can contain a few 10,000 to a few 100,000 transistors. On top of that, engineers made these components programmable. This comes down to using components whose functionality changes all the time (essentially at the rate of their clocks, often measured in MHz or GHz). The programs they run are composed of elementary instructions, meaning that the use of programs increases the size of the state machine exponentially. How do we ensure that such systems can be trusted to be correct?

This is not an easy task. Before electronics, most systems were analogue or mechanical ones. Such systems often require a lot of energy and are bulky, but usually they are quite trustworthy. The reason for this is that such systems inherently provide what is called "graceful degradation". Their state space is continuous and hence infinite, but when the material properties are affected by e.g. wear and tear, a mechanical system will keep delivering its function, even when it will have become less efficient. This is the property of graceful degradation. Of course, at some state, the system will break down as well, but there will be ample warning (if one cares to look and listen).

Digital electronic systems are often designed and manufactured in such a way that each individual transistor remains in a safe domain over its anticipated lifetime, just like with mechanical system. The difficulty comes from the fact that in an electronic system, these transistors are connected and therefore they create a large state machine. When a single transistor or its connections to another transistor fails for some reason, the system might continue to work but there is also a non-zero probability that the failure will bring the whole system to a halt. Often this means it goes into an illegal, read: undefined, state. Fortunately, in (small) digital electronics the state space is still combinatorial and in principle, one can simulate the system across all these states or one can even design a test set-up that will exercise all possible states, allowing to verify that the design prevents the system from reaching such an illegal state, even if such an event is very unlikely under normal operating conditions. The issue is that reaching such an illegal state can become very likely when the operating conditions are no longer "normal" (e.g. because the external conditions put the device outside its normal operating conditions). Often, the result will be catastrophic.

The problem really becomes horrendous when we look at embedded software running on such an electronic component. The issue is that now the size of the state space is exponentially expanded. This is partly due to the way software instructions are encoded in the hardware. If a single bit is changed, the behaviour can become entirely different. In addition, programmable electronic components are often built as so-called von Neumann machines. The processor instructions are executed in sequence. The program will also contain branching points, meaning that the resulting state space can grow very large, even under normal operating conditions. Moreover, embedded software will often not have the property of graceful degradation. If for some reason the next instruction is not the right one, the system can come to a halt in nanoseconds and standard processors cannot recover from such errors. A hard reset and rebooting from the beginning is often the only sensible option. Most of us are familiar with this notion, often called a "blue screen", but very few know that an ordinary PC will have at least one memory bit flipped per day due to cosmic radiation. While this is often innocent, when such an event occurs in a safety critical system, lives can be at stake.

Given that the state space is now exponential and that it is physically impossible to test all possible states, how can we then have confidence in embedded software? The solution engineers adopt is to prove that the software will be correct (this holds under the assumption that the hardware is correct as well). This is essentially not different from what engineers do in other domains. For example, construction and material engineers will often not test their construction to see when it will fail. No, they will develop a mathematical model and calculate the breaking point based on the assumption that their raw materials were correctly manufactured. This allows them to apply a hefty safety margin to their design. Unfortunately, software cannot be made robust by adding somewhere a safety margin, hence we must "calculate" it exactly. This is what the emerging field of formal techniques is all about and this book is about its application to the development of a crucial embedded software component: a network centric Real-Time Operating System.

Another aspect is that the development of embedded software is not a "standalone" activity. Embedded application software has many dependencies, often on third party input or components. In addition, embedded software is essentially implementing a real-world context as a computer program. If the description of this real-world context is erroneous, these errors will be found back in the resulting application software and there they can result in erroneous products even if the implementation of the software was done correctly.

Therefore, we need to look at the whole systems engineering process. This is essential to develop trustworthy products because engineering a product involves a lot of human activity. It is a complex process with many aspects and many problems that need to be mastered. One of them is the use of natural language. Because natural language is not precise enough, often vastly differing between cultures and different domains, it is the source of many issues in systems engineering. Therefore, we must try to achieve a common language across all domains that are involved in the engineering of a product or a system. We called this trying to achieve "unified semantics". The only way to do this is to develop a unified "systems grammar" as we call it, that covers the full domain of systems (or software) engineering. This is similar to the development of an ontology but it adds the notion of "interaction" to make the relationships between the concepts concrete from early requirements to the final release of the product or system being developed.

Just like in a language it defines terms of a vocabulary and relationships between these terms. Such a systems grammar will also seek orthogonality, essentially trying to come up with terms that have no overlapping and no ambiguous meaning. Less is often better in this context. It can be understood as an application of Einstein's principle (or occam's razor if you prefer). Keep things simple, but not too simple. Essentially, if a solution is complex, it is not because its creators were smart, but because they did not fully understand the problem at hand. Below follows a description of the systems engineering methodology we developed and of which the OpenComRTOS project was at the same time a test case as well as an important key component of the supporting environment.

#### **1.2 A Systematic Engineering Methodology Based** on Unified Semantics and Interacting Entities

Generally speaking, systems engineering starts with what is called "requirements and specifications capturing". This is a domain where many people, called stakeholders, are involved. In a first instance they formulate, often more informally than formally, "requirements". Requirements are often not precise enough to serve as a basis for implementation. They will often be contradictory, overlapping and stretch across multiple, very divergent domains. To find out which requirements are really relevant and what they really aim for requires a lot of social interaction and discussions (Fig. 1.1).

Often, the term "requirement" is wrongly used to indicate what good systems engineering calls "specifications". A specification is defined as a quantified or qualified requirement statement. This means it is linked with measurable values, generally called verifiable properties. When we say "verifiable" we can design the system to achieve the specified properties. A consequence is that we also have to specify how we will measure, verify and test the specified properties as the methods we use will often influence the result. We call this the "test case". This is a first domain were standardization might be useful to reduce the guess work and to increase the repeatability of the process. Another aspect is that we need to specify the circumstances under which the specifications will be met. The fact that a specification is linked with measurable values indicates that there must be one or multiple test cases, which means that the design must take the test conditions into account. The test case will often only be present when testing but it will often require the design to have provisions for it.

In normal operating conditions, we speak of the "normal" case. But as we have seen earlier, undesired behaviour often happens in conditions that are unlikely and often outside the normal operating parameters. This is called the "fault case". Thinking about fault cases is difficult because it requires to think in reverse: "if the system fails in a certain way, what type of failure could that be and what chain of events could cause it?".

Next comes the step where the specifications are realized by a concrete design. Although often it will be required that the system is implemented using previously developed or reused components, the difficulty here is not to let the implementation choice influence the specifications. In the ideal world, the engineer will now build several "models". Models are essentially partial implementations that fulfil selected specified properties of the system. We distinguish here three classes. Simulation models are essentially virtual prototypes of parts or of the whole of the system as

Fig. 1.1 Unified Systems Engineering Methodology

computer models. Often modelling tools will be used which allow the designer to develop such a simulation model in a relatively short period of time. Simulation models are used to verify first of all that the requirements and specifications were correctly understood and analysed. They also allow to do quick "what-if?" analyses. Furthermore, this activity will result in improved requirements and specifications as it will contribute in further insight in how the system will behave under the fault and test conditions. Simulation models have another benefit: often they are a lot less expensive to develop than the real system and making a change has a lower cost than having to change a real prototype or working system.

If the project constraints allow it; one or more architectural models will be developed. In the ideal case and if the domain and the tools allow it, architectural models should be deduced automatically from the simulation model. After a tradeoff analysis the best simulation model will become the implementation model. Architectural modelling will always benefit from being expressed in the highest possible level of abstraction, often domain independent, with the lower levels details being generated by a domain specific "compiler". It is assumed that this compiler is efficient enough for its output to be economically acceptable.

Finally, while a simulation and an architectural model allow us to reason and think about the system, they provide no proof that the system under development will be trustworthy. To verify this for critical properties (e.g safety related ones), formal techniques can be used. Formal models can be considered as a special case of simulation models. Often, formal techniques will result in fairly abstract models of parts of the system that can be fully automatically analysed and proved by formal model checkers. Such model checkers automatically traverse the whole state space and herein lie their strengths as well as their limitations. The formal model must be small and abstract enough to allow a complete model check in a reasonable amount of time (and memory resources). In the alternative, formal proving techniques can be used, but they require higher mathematical skills and are rather labour intensive. When used however, they can greatly increase the trustworthiness of the system.

Specifications are normally fulfilled by parts of the system being developed. For example, if the requirement of a radio receiver specifies a quality assessment for the signal in the presence of noise, the deduced specification will state a signal to noise ratio with a specific value expressed in dB and to be reached in a certain frequency band. One of the parts of the system that will be implemented to achieve these figures could be a filter component. In the methodology we call a subsystem component that realizes the specification an "entity", an abstract term for any part of the system. Developing such a subsystem entity might be a project on itself, for example a processor chip will be a component of a larger system but when the package is opened, it will show to be a complex system as well, albeit with much smaller physical features.

All subsystem entities together create the system because they interact. The system properties will be the result. Often, it makes sense to distinguish an interaction as a separate conceptual entity, especially if physical properties have to be taken into account. In general, entities and interactions can cross many different domains. For example, a light sensor will transform light energy from the environment into an electrical current. This sensor might have been mounted on a mechanical shaft so that it measures a position. The electrical signal can be used by a programmable controller that transforms the analogue signal into a digital one, calculates in software (or in hardware) a steering value that is transformed again into an analogue signal that is applied to an actuator that transforms the electrical signal into an hydraulic pressure. If one follows this chain, one can easily differentiate multiple entities and interactions of different types. At an abstract level however, we only see information, matter or energy being transformed and passed on between entities. If we would write a software simulator, it would be enough to have the equations or use the same message passing primitive. One might even replace the sensor by a software process running on the controller without changing the functionality of the rest of the system.

The latter is a crucial observation. Requirements and specifications express properties about the system without a reference to how they are realized. Entities and interactions express the architectural composition of the system. Expressing and analysing this is often called modelling. However, for this modelling to work smoothly, it is clear that it should be straightforward to move from one domain to another. Given that the real world is naturally expressed as sets of interactions and entities, it is straightforward to use the same paradigm everywhere, in particular for developing the architectural models and a selected implementation.

#### **1.3 Interacting Entities for the Software Domain**

Given that software programs are essentially computer models of real-world concurrent systems, and that real-world systems can often be described in terms of interacting entities, would it not be natural and beneficial that computer programs reflect this as well? Unfortunately, this is seldom the case. Most programs are written as a single long sequence of instructions, even if embedded systems technology allows for asynchronous interactions with the environment through an interrupt mechanism. One of the reasons for this lack of concurrency in the program is that the most widely used programming languages (C in the embedded case) have little or no support for concurrency. The fundamental reason is that processors evolved all from the sequential von Neuman machine architecture and that programming languages were developed bottom-up, from the hardware to the software and not the other way around as good systems engineering would have prescribed. The underlying issue for developing reliable systems is here again the state space. By keeping things sequential, the whole state space is exposed to the application layer and the larger the program, the higher the probability that a single error or fault can bring the whole system to a halt.

Nevertheless, in the embedded world, solutions were developed that addressed some of the issues. Concepts like multi-tasking and inter-task synchronization can be found in what we call RTOS (Real-Time Operating Systems). They were introduced as a means to decouple the timing behaviour from the functional behaviour in an embedded system, even at first sight at the cost of a little overhead. In embedded systems, real-time requirements are measured in microseconds and achieving predictable real-time properties while using big loops is very difficult, certainly in an implementation independent way. This must be seen in contrast with the desktop world, where the available computing power is much more abundant, but were real-time constraints are often very flexible and measured in terms of human perception. For vision this is around 40 ms but often even a few seconds can be acceptable.

Currently, several forces are converging to make concurrency in programming feasible as well as desirable.

#### 1.3.1 Silicon Technology Advances

Contrary to may other domains, in electronics the rate of technological progress has been phenomenal. Engineering has succeeded more or less in quadrupling the amount of transistors on a given square millimeter of chip surface every two years. This means that higher clock rates, lower power consumption and functionality have evolved along similar lines. At the same time, this has made it rather straightforward to start putting multiple processors in a single device.

However, this has created a software productivity gap. Software is still largely being developed by the same human brains as 50 years ago using more or less the same (sequential) programming languages. Concurrent programming helps on several levels:

- Mastering the complexity: dividing the application in a number of smaller, more or less independent entities, breaks up the state space into smaller chunks as well.

- Greater reuse: when functions are programmed as concurrent tasks or processes with clearly defined interfaces (not through a shared state space but through protocol based message interaction), such software components can be reused with a plug-and-play technique even across multi-processor systems.

- Increased complexity of applications also means that larger software teams are needed. Again, concurrent tasks or processes can then be developed as components allowing to distribute the work.

- Increased need for reliability: as outlined above, the major issue for achieving reliability is the state space size. By confining the state spaces, we can limit the impact of an error to a smaller part of the system, especially in combination with hardware protection mechanisms in the programmable hardware.

#### 1.3.2 Silicon Technology Limitations

The increased processor speeds do not fully result in an equal performance increase at the application level. Programs essentially transform data that is stored in memory and save it back to memory. However, memory technology does not scale as well as processing technology for size and access speed. Hence, when the data is in external memory, often the CPU will have to wait for hundreds of clock cycles. And while all kind of micro-architectural 'tricks' like caches, pipe-lining and other are in use to alleviate the performance gap, they do not address the core problem of real-time predictability and power consumption.

With increasing chip size, a bottleneck also appears on the chip itself. Most chips still use a single master clock and given the high density of the chips, it becomes increasingly difficult to distribute the clock signals across the whole chip. A natural solution is to define multiple concurrent clock domains. As it has become a lot simpler to implement fast communication channels between processor cores, even when going off-chip, a concurrent architecture emerges at the hardware level. As a result, depending on the computation to communication ratio of the applications as well as of the available hardware, it becomes feasible to achieve better application level performance using multiple slower processors rather than using a single very fast one. It saves on energy and it also saves on connection pins, often one of the most expensive parts of a packaged chip. The precondition is that applications are from the start designed in a way that they can easily be distributed over multiple processors. An additional benefit is that the system will consume less power and slower technologies, costing less can be used.

#### 1.3.3 The World Becomes Connected

Advances in technology (in the software as well as the hardware domain) have also resulted in a major change in the way systems are deployed. The world became wired and internet allows to establish connections to almost any point in the world. In this world, a lot of existing technology has already been deployed and it is mandatory to connect with legacy systems in symbiosis. Again, a programming model that assumes concurrent and distributed platforms from the beginning makes this a lot easier to achieve.

As a conclusion, we can say that there are many reasons why a concurrent programming model is a natural one. It fits much better with engineering design activities like modelling and it fits best with the change in technology. This book describes a programming model that actually achieved this goal of universal (concurrent) programmability.

#### 1.4 A Link with the Work Plan in a Systems Engineering Project

Finally, when all requirements, specifications and models have been developed we still need to plan to develop the product in a systematic way. The result is a work plan and typically the subject of "project management". Often, this work plan will start when specifications have been frozen and the design has been selected. Note that the activities we defined above as well as the development will not occur in a sequential order. A good engineering process should be iterative because every activity will allow discovering issues that were not considered before. This is also teamwork, with each team member providing a specific view on the system being developed. For this iterative process to take place, development should also be grouped into sufficiently small work packages with each task being small enough to keep an overview. Given the decomposition into entities, an entity or a group of related entities becomes a natural way of distributing the work to be done.

We define a Work Package as a group of related tasks that together achieve the implementation of a number of entities. We distinguish four main types of tasks, this distinction is important in the context of formalized development. The first type is the development task itself. Using specifications and the developed models, this type of task will develop the subsystems that as a whole result in the final system. If the modelling tools are powerful enough, then the implementation can often be generated. If not, a tedious work of manual coding may be needed. In order to verify that these development tasks were done correctly (e.g. as defined by a procedure) a verification task is defined. It will not verify the subsystem itself, but mostly verify that it was correctly developed. Once that is done, the developed entity can be tested in a test task according to the defined test cases together with the specifications. Finally, when all developments have been verified and the results tested and approved, everything can be integrated and validated against the requirements in a validation task. Again, the architectural paradigm of interacting entities will help here because it provides separation of concerns and they help to tackle the complexity.

#### **1.5** System Engineering Methods and Engineering Standards

It is interesting to have a look at how professional engineers today achieve high reliability. Standards for system (and software) engineering exist and were developed to meet the requirements of developing complex (and hence costly) and often safety critical systems. Typical examples are found in the aerospace and transport sector. The standards were partly developed to achieve a more predictable and repeatable engineering process. Combine this with the need of certification by external third parties and most of these standards read like complex and confusing recipes.

If one reads these standards, one will notice that formal methods are mostly absent although when using them the developer gets "extra points". For the highest safety integrity levels they are a must in the sense that their use is required to prove for example that the software is correct under all circumstances. Most of these standards are also not very prescriptive but they list a large number of activities that should be taken when developing a safety critical system and they are used as a basis for certification. At this stage one must consider that such standards are first steps away from fully heuristic development towards fully formalised developments away from fully heuristic developments. Their use will certainly improve the resulting trust in the developed product or system but it is not a sufficient condition. We believe that as experience and education grows, formalisation of the system engineering process will increase followed by the development of cleaner and leaner process models. For example while IEC-61508 is considered the mother of safety engineering standards, it is almost impossible to apply with a lot of guesswork. On the other had standards like ISO-26262 and DO-178B are a lot more readable and define a more logical process. In the future we can also expect standards from different domains (e.g. aerospace, defense, railway, automotive) to merge. After all good systems engineering is not bound by a domain, although domain specific heuristics remain important as well.

#### **1.6 Where Do Formal Techniques Fit in?**

Traditionally, formal techniques (or formal methods) are seen as a technique to prove that e.g. a certain piece of critical software is correct. It must be understood that this is only partially possible because there are many dependencies. First of all, software is most often written in a programming language that was not formally defined and for which the compilation tools were not formally developed, neither is the processor developed and verified in a formal way. Hence, the programming language and the compilation tools are trusted on the basis of real-world use and extensive testing. A second issue is that the translation between the formal, often more abstract models and the programming language will never be "perfect". While formal techniques force us to specify and think about every fine grain level detail, at the same time they allow us to abstract away from the real world artefacts often introduced during a heuristic development process. Hence, one can prove that the formal model was correct, but that does not prove that the software as an implementation of the formal model is correct. Nevertheless, using these techniques can greatly improve the trustworthiness in the final system, partly because formal techniques force us (or rather allow us) to think more upfront about all possible states and ways to construct the system.

Considering the iterative systems engineering methodology described above, it is clear that formal techniques can be used in any stage of the process. The reason is that they help to reason about the system at a more abstract level with less interference from the heuristic knowledge that goes with implementation. This has proven to be a crucial factor in the formal development of OpenComRTOS. Because formal techniques were used from the very beginning to develop the architecture, several issues were detected that would not have been found after the implementation. It also allowed to develop a much more efficient and cleaner architecture, highlighting an aspect that is often neglected in systems and software engineering. An efficient architecture is the equivalent of a better algorithm. Whereas a better algorithm will often result in more efficiency for a specific property (performance, power consumption, etc.) a better architecture has often wider ramifications like being easier to use, easier to reuse and easier to adapt to other purposes. In this project, it even results in a much smaller code size (5-10 times smaller) than what previously had been obtained using traditional manual development. This is remarkable as an RTOS has always been perceived as a complex and difficult piece of software requiring the use of "hackers" to get it right. The formalized approach we took using formal methods did better without requiring extra resources and time.

Finally, it must also be said that one has to consider formal techniques as a crucial but not the only factor contributing to a trustworthy and optimized design.

After all, engineering is a human activity and there are many aspects and views that need to come together. Our experience showed that intensive team work is very beneficial, especially when combined with "formalisation". Formalisation serves two purposes. Firstly, it forces the participants to formulate their thoughts clearly while exposing the hidden assumptions. Secondly, the formulated concepts have to be made much more concrete and unambiguous. This allows to share the semantics which means that it becomes easier to discuss the system to be developed without guesswork filling in the gaps. Formalisation in itself will often be helpful in finding reasoning errors (typically finding unwritten assumptions) and the same procedure of formalization is also the necessary step toward the use of formal techniques. The latter can be considered as the next logical step in formalisation by translating the model in a format that makes it susceptible to mathematical analysis. This will in itself restrict the interpretation that can be given to the concepts used in the formal model but this is necessary to take control and to allow automated model checking.

## Chapter 2 Requirements and Specifications for the OpenComRTOS Project

In this chapter, we discuss the requirements and specifications for the OpenCom-RTOS project from the point of view of its capabilities to support applications in meeting real-time requirements. As this is related to a distributed real-time operating system this is rather unique as most RTOS are designed for single processor systems and if not, they assume a shared memory architecture whereby the address space is global. OpenComRTOS on the other hand makes no such assumptions, but assumes that a processor has local memory and that the hardware allows to communicate somehow between the processors' memory. It is a network model, but allowing to emulate it by shared memory if this is available. Hence the term "network-centric" RTOS. In this context, we also explain the CSP background that is still present in the conceptual design of OpenComRTOS.

#### 2.1 Background of OpenComRTOS

The initial purpose for developing OpenComRTOS was to provide a software runtime environment supporting a coherent and unified systems engineering methodology based on "Interacting Entities". This was originally developed by Open License Society, (OLS 2011) and currently further developed and commercialised by Altreonic, (ALT 2010). In this methodology, requirements result in concrete specifications that are fulfilled in the architectural domain by concrete "entities" or sets of entities. Entities can be decomposed as well as grouped to fulfil the specifications. In order to do so, we also need to define "interactions", basically to coordinate the entities synchronise and exchange data, at least in the domain of embedded systems. The approach, however, is universal and the same view holds for other domains as well, e.g. business processes or mechanical systems. The difference is in the physical nature of the interactions and entities and in the terminology used. Interactions and entities are first of all abstractions used during the modelling phase. As such, a specified functionality can first be simulated as part of a simulation model,

Fig. 2.1 The context of systems engineering

critical properties can be formally verified using formal techniques and finally an implementation architecture can be defined using the architectural modelling tools of the target domain. In our case, we try to keep the semantics unified from early requirements till implementation. In the targeted embedded systems domain, this means that the final architecture is likely a concurrent software program running on one or more programmable processors. Some functionality might be implemented in specific hardware entities. Such entities will be integrated in the input or output subsystem or will be designed as co-processing blocks. In most cases, these hardware entities will be controlled from software running on a processor.

In an embedded system, and in most systems, two additional systems must be taken into consideration, as illustrated in Fig. 2.1. The first one is the "environment" in which the embedded system is placed. This will often generate inputs to the system or accept outputs from it or it will influence the operating conditions, not necessarily in a fully predictable way. A second system that is often present is the "operator", who also will generate inputs or act upon the outputs. If this is a human operator, we have to deal with an entity who's behaviour is not necessarily always predictable. Often, the "operator" might be another embedded system and then the behaviour should be more predictable, at least if well specified. However, systems are layered. If we "open" the embedded system or consider the system under development with its environment and its operator as a new system, we can see that each system can be a components". For this book, we stay at the level where such components are programmable processors.

The use of a concurrent programming paradigm embodied in an RTOS is then a natural consequence of the unified semantics paradigm. Programming in a concurrent way implies that the abstract entities (that fulfil specifications) are mapped onto RTOS "Tasks" (also called processes or threads in the literature) and that interactions are mapped onto services used by the tasks to synchronize and to communicate. In principle, this abstract model equally well maps to hardware as to software but we focus here on the software. The target domain ranges from small single chip micro-controllers over multi-core CPUs to widely distributed heterogeneous systems that include support for legacy technology. OpenComRTOS should allow to program in a transparent way such a target system, independently of the processor or communication medium used. In the context of the OpenComRTOS project, an additional requirement is related to the process used for developing OpenComRTOS. Given the importance and generic nature of a RTOS as runtime layer, we considered it important that the resulting RTOS would be safe, correct and performing. Hence, it was a requirement to use formal techniques for its design as well as for its verification.

#### **2.2 Early Requirements Derived from the Virtuoso RTOS**

Following the requirements, we can in principle derive the specifications. However, specifications cannot be fully separated from implementation choices. In our case, a previously developed RTOS called Virtuoso (Verhulst 1993a,b, 1997a,b, 2002) served as a guideline.

In this section we first analyse it, highlighting issues as well as benefits of the then existing architecture. Virtuoso was a distributed RTOS, developed by Eonic Systems until the technology was sold to Wind River Systems in 2001. Its main target was parallel DSP systems, although it has been ported to other architectures in single as well as in multiprocessor versions. Even heterogeneous target systems have been demonstrated albeit at the expense of a lot of manual integration work. The smallest system it had been ported to was an 8bit micro-controller in a telephone handset, the largest system was a system with over 12,000 processing nodes, heterogeneous but built up as a number of homogeneous clusters. The experience with Virtuoso was crucial. It also taught us the limits of such a programming environment. These limits lay not so much in the RTOS itself but in maintaining and supporting it. As such the porting effort was high because of the complex and optimised architecture and it was very difficult to add functionality. Nevertheless, its overall functionality of transparent parallel processing (this was called the "Virtual Single Processor" runtime model) (Verhulst and De Jong 2007; Verhulst et al. 2008) was a major driving force to redevelop it in a better way. Hence, to some extent, OpenComRTOS is conceptually a fourth generation of Virtuoso although it was a clean room development. At the outset we were curious to see how we could do better but it was totally unanticipated we would be able to improve it beyond all initial expectations.

The Virtuoso RTOS had its origin in the pioneering INMOS transputer (Wikipedia 2011; INM 2011), a partial hardware implementation of Hoare's Communicating Sequential Processes (CSP) process algebra (Hoare 1985a) masterminded by Dr. David May. Later on Virtuoso was ported to traditional processors but mostly parallel DSPs. The transputer was a rather unusual RISC like processor with unique support for on-chip concurrency and inter-processor communication. Onchip it had a scheduler with two priority levels, each level supporting round-robin scheduling between the compile time generated processes. It also had hardware support for inter-process communication and synchronization using "channels". For distributed, embedded real-time applications, it raised two major issues:

- Two levels of priority are not enough for hard real-time applications. Typically, at least 32 levels of priority are needed and full support for pre-emption and priority inheritance.

- Topology independence: although the transputer had interprocessor links, the communication between processors had to be manually routed at the application level. The issue is here mostly one of maintenance. Every little change in the topology could result in major reprogramming efforts.

Although the transputer hardware and available software (like occam and parallel C) were derived from the CSP process algebra, the use of processes and channels was very novel and hence this was a stumbling block for wide adoption by the embedded market. That and the failure to develop a successor product (there was one but it was over-specified for the silicon technology available at the time) resulted in the demise of INMOS, the company developing it. Nevertheless, it lives on as a set-top box controller from ST Microelectronics and the link technology is now adopted as a standard by the space sector (IEE1355 enhanced with LVDS signalling and subsequently called SpaceWire), see (Spa 2011; IEE 2011). One of the closest successor chips today is the XMOS chip, see (XMO 2011), also a brainchild of David May. While the CPU is a more convential RISC processor, it has support for hardware assisted multi-threading (up to 8 threads/core) and a single chip contains from 2 to 4 CPU cores.

The above observations resulted in the adoption in the Virtuoso RTOS of the following architectural principles:

- Use of 255 levels of priority with full pre-emption capability.

- Development of traditional RTOS services like events, semaphores, fifos, mailboxes, resource and memory maps.

- System wide identifiers used for transparent system wide routing.

- Use of command and data packets to provide topology independent programming.

- Packets carrying a priority inherited from the generating task.

- Support for priority inheritance in the scheduler (see further).

When Virtuoso was ported for the first time to a parallel DSP target, it was found that a major redesign was needed. While the links on the transputer could be accessed by memory mapping the internal channels to an I/O address, DSPs provide the programmer with a series of "raw" I/O ports. The challenge here is that the communication on these ports is interrupt driven, often with DMA engines operating in the background. On the Texas Instruments TMS320C40 DSP or Analog Devices 21060 DSP for example, this resulted in 12 interrupts and 2 timer interrupts that were independently enabled. Hence, there was a need to develop a low latency driver architecture. This was achieved by developing a specific system level nanokernel that was mainly written in assembler and used a subset of the processor context. While it provided very fast communication handling, it had the drawback that porting it to another processor was a major effort.

Later on, Virtuoso was also extended with new features and services. However, these were at the expense of performance while the code size was rapidly growing. Another observation was that this resulted in some errors that could remain dormant for years until an unanticipated usage triggered them.

Combining all these experiences resulted in some decisions at the architectural level that are found back in the OpenComRTOS requirements:

- General use of packets at all levels

- Prioritisation at all levels (local scheduling as well as at the communication layer)

- · Support for distributed priority inheritance

- Support for traditional RTOS services (events, semaphores, fifos, etc.)

- General use of ANSI-C, minimising the use of assembler (hence no nanokernel)

- Modular architecture allowing to remove or add functionality without affecting the rest of the system

- All services to be formally modelled and verified

At the start of the OpenComRTOS project, these were not firm requirements. As the reader will see, the use of formal techniques in the project has allowed it to go way beyond the functionality of Virtuoso. Although it was known as highly performant and small in code size, we were not expecting to be able to do much better, except in having a cleaner and safer RTOS.

### 2.3 Real-Time Embedded Programming

While most programming is concerned with performance (often expressed in terms of achievable throughput), real-time is then often equated to "fast enough". In the embedded domain, however, the system will often interact with the physical world whereby stringent time requirements must be met or the system can fail. In such systems, the reactive behaviour is most important and must always be achieved independently of the logical correctness of the application. Such systems are often called "hard" real-time in contrast with "soft" real-time systems where time properties are statistical.

### 2.3.1 Why Real-Time?

It can be argued that an architectural paradigm based on entities and interactions does not need any notion of real-time. Indeed, the time properties can be considered as mostly orthogonal to the "logical" behaviour of a system. In the embedded domain (and most of the systems we use have embedded aspects), we are dealing with real-world interaction and time is part of it. Signals that the embedded system must process arrive in real-time and must be dealt with before the next set of signals arrives. Similarly, the embedded system will act on its surroundings and real-time requirements apply. Implicitly, we assume here that sampling theory is applied. Sampling theory dictates that we should at least sample at twice the bandwidth of the signal. Similarly, when we apply output or control signals this must also be done with a rate at least equal to twice the bandwidth. If the controlled subsystem has a mechanical mass and physical properties such that inertia determines the dynamic behaviour, we must similarly take into account its time constant. Sometimes, the output timing can be rather demanding. An example is audio processing. The human ear is very sensitive to phase-shifts so that even when the bandwidth requirements are met, the jitter requirements are stringent enough that hardware support might be needed.